因為專業

所以領先

堆疊芯片封裝工藝流程分析

一、核心工藝流程

芯片制備與減薄?

原始硅片通過化學機械拋光(CMP)或干式/濕法腐蝕減薄至50-100μm,以降低后續堆疊厚度并提升散熱效率?。

減薄后通過激光/金剛石刀片完成劃片,形成獨立裸芯片,切割過程需控制邊緣微裂紋以保障機械強度?。

堆疊結構實現?

PoP(Package-on-Package)?:

① 底部封裝(如邏輯芯片)采用倒裝焊(Flip Chip)貼裝至基板,完成底部填充(CUF工藝)?。

② 頂部封裝(如存儲芯片)通過錫球與底部封裝垂直互連,形成整體封裝?。

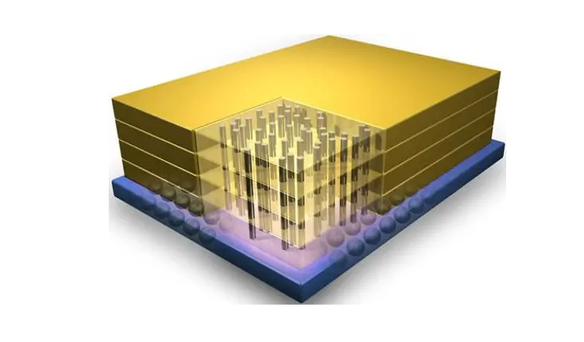

TSV(硅通孔)堆疊?:

① 在芯片內部通過深孔刻蝕形成TSV,填充銅/多晶硅實現垂直導電通道?。

② 多層芯片直接堆疊并通過TSV互連,結合微凸點(Microbump)技術提升密度?。

互連與鍵合技術?

熱壓鍵合?:高溫高壓下實現芯片間微凸點焊接,確保電氣連接可靠性?。

混合鍵合?:結合銅-銅直接鍵合與介質層融合,適用于高密度互連場景?。

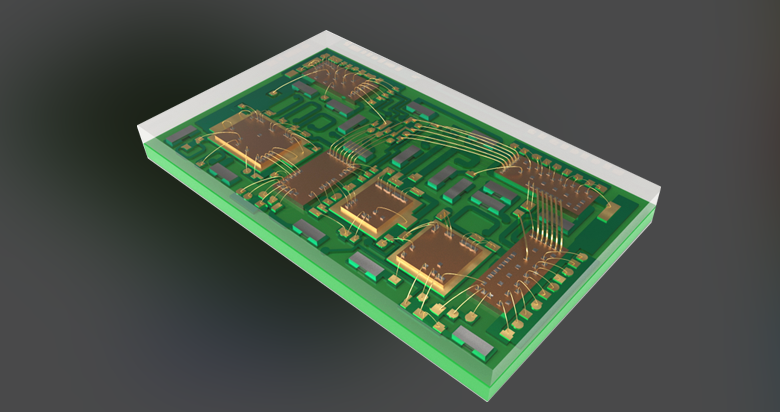

線鍵合?:傳統金線/銅線連接用于非TSV堆疊的芯片級互連?。

封裝成型與固化?

采用環氧模塑料(EMC)通過轉移成型工藝完成塑封,固化溫度控制在175-185℃以降低熱應力?。

扇出型封裝(如InFO)省去基板,直接封裝芯片于樹脂層以提升I/O密度?。

后段處理與測試?

去飛邊/毛刺:機械或激光修整塑封體邊緣?。

電性測試:通過探針臺驗證堆疊芯片功能及互連完整性?。

二、關鍵技術挑戰

熱管理?

多層堆疊導致熱阻疊加,需嵌入微流體通道或采用高導熱底部填充材料(如納米銀膠)?。

信號完整性?

高速TSV互連需優化阻抗匹配,通過屏蔽層設計降低串擾?。

機械應力控制?

不同材料熱膨脹系數差異引發翹曲,需使用低模量底部填充膠及應力緩沖層?。

良率提升?

采用AI驅動的缺陷檢測系統優化TSV刻蝕和鍵合工藝參數?。

三、典型技術方案對比

技術類型 工藝特點 應用場景

PoP封裝 分體式封裝堆疊,兼容不同制程芯片,靈活性高 移動設備處理器+存儲器?

TSV 3D堆疊 芯片級垂直互連,延遲低至皮秒級,帶寬達TB/s HBM集成、AI加速芯片?

混合鍵合堆疊 銅-銅鍵合間距≤5μm,密度提升10倍,但工藝復雜度高 高性能計算芯片?

四、發展趨勢

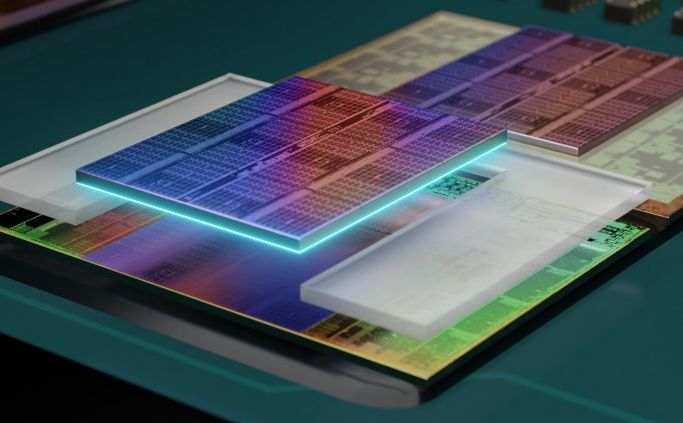

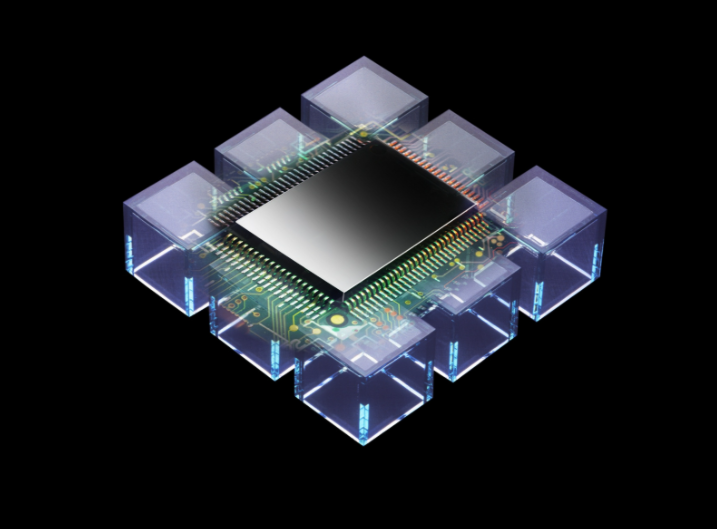

Chiplet異構集成?:通過先進封裝整合多工藝節點芯粒(如7nm邏輯+28nm模擬),降低整體成本?。

晶圓級封裝?:直接在晶圓上完成堆疊與互連,減少單體封裝工序(如臺積電CoWoS)?。

![[x]](/template/default/picture/closeimgfz1.svg)